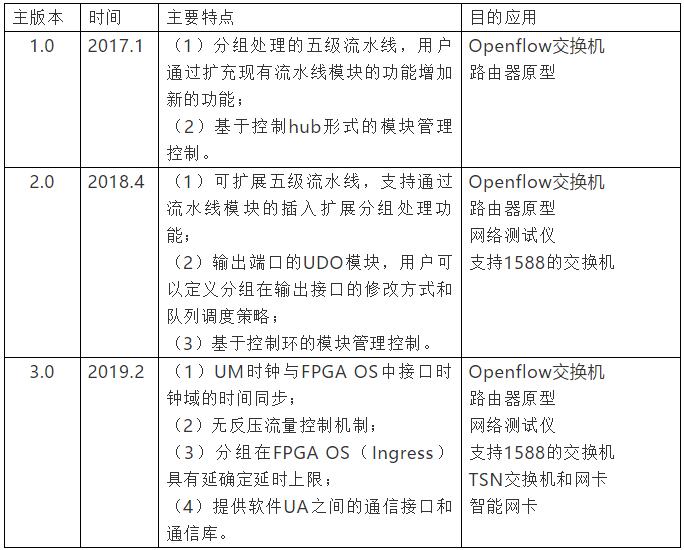

2017年推出的FAST 1.0規範主要支持OpenFlow交換,2018年推出的FAST 2.0規範在優化流水(shuǐ)線管理(lǐ)配置的同時(shí),擴展UDO模塊以支持IEEE 1588透明(míng)時(shí)鐘(zhōng)計(jì)算(suàn)和(hé)網絡測試儀(FAST-ANT)精準的發包控制和(hé)輸入分組時(shí)間戳标記。2019年FAST将進一步優化FAST 硬件流水(shuǐ)線以及FPGA OS的架構,推出3.0規範,以支持時(shí)間敏感網絡(TSN)的交換需求。

一、需求背景

時(shí)間敏感網絡(TSN)是工(gōng)業互聯網和(hé)關鍵行業領域實現(xiàn)确定性交換的重要手段。在2018年工(gōng)信部發布的《工(gōng)業互聯網發展行動計(jì)劃(2018-2020)》中,明(míng)确提出“在汽車、航空(kōng)航天、石油化工(gōng)、機械制造、輕工(gōng)家電、信息電子等重點行業部署時(shí)間敏感網絡交換機和(hé)工(gōng)業互聯網網關等新技術關鍵設備”。

近年來(lái),IEEE 802.1工(gōng)作(zuò)組不斷推出新的TSN标準,在802.1Q标準的2018年版本中增加了(le)大(dà)量對(duì)2014版本的修訂,而針對(duì)2018版本的更多TSN相關修訂還在制定過程中。由于ASIC芯片具有至少兩年的研發周期,因此目前成熟的網絡芯片難以符合最新的TSN規範,FPGA在TSN市場内大(dà)有可爲。

二、FAST 2.0規範的不足

2018年6月推出的FAST 2.0規範增加了(le)用(yòng)戶定義輸出控制(UDO)模塊規範,支持網絡接口對(duì)IEEE1588規範定義的PTP分組(sync/delay_req/delay_resp)透明(míng)時(shí)鐘(zhōng)的處理(lǐ),然而FAST 2.0規範還難以全面支持TSN交換設備(TSN網絡接口控制器和(hé)TSN交換機),主要表現(xiàn)在:

(1)缺乏FPGA内部多時(shí)鐘(zhōng)域的時(shí)間同步機制

FASTFPGA内部的UM邏輯和(hé)FPGA OS内部的每個網絡接口的收發邏輯處于不同的時(shí)鐘(zhōng)域,FAST 2.0沒有提供這(zhè)些(xiē)異步時(shí)鐘(zhōng)域中時(shí)間的同步機制,因此難以精确計(jì)算(suàn)PTP分組從(cóng)UM發出時(shí)刻與該分組從(cóng)網絡接口發出時(shí)刻之間的時(shí)間差值,造成時(shí)間同步的誤差加大(dà)。

(2)FPGA OS和(hé)UM之間的反壓機制難以支持分組的确定性轉發

FAST2.0與1.0一樣,UM與FPGA OS之間采用(yòng)單個優先級的反壓流量控制機制,這(zhè)就會(huì)造成分組在FPGA OS和(hé)UM内部的轉發延時(shí)不可控,特别是低(dī)優先級的分組可能(néng)會(huì)阻塞時(shí)間敏感分組的轉發延時(shí),難以滿足TSN标準中的CQF(cyclic queue forwarding)功能(néng)。

(3)缺少1588時(shí)間同步的實現(xiàn)模型

FAST2.0支持交換機的透明(míng)時(shí)鐘(zhōng)操作(zuò),但(dàn)難以支持1588同步中的時(shí)鐘(zhōng)master和(hé)slave端的操作(zuò),缺少UM核心時(shí)鐘(zhōng)的調整機制,因此無法支持TSN全網設備時(shí)間同步的需求。

三、FAST 3.0的特點

FAST 3.0在全面兼容FAST 2.0硬件UM和(hé)UDO設計(jì)的基礎上(shàng),在以下(xià)兩個方面對(duì)FAST 2.0進行升級。

(1)FAST UM核心時(shí)鐘(zhōng)與外(wài)圍I/O時(shí)鐘(zhōng)同步方案

由FAST UM維護核心時(shí)間計(jì)數器,在UM接口規範中增加全局時(shí)間輸出相關信号,支持FPGA OS中外(wài)圍接口時(shí)鐘(zhōng)域與UM内部的核心時(shí)鐘(zhōng)進行同步。

(2)提供IEEE 1588同步master/slave模塊

提供标準的可插入FAST流水(shuǐ)線中獨立工(gōng)作(zuò)的IEEE 1588時(shí)鐘(zhōng)同步模塊,根據配置支持主時(shí)鐘(zhōng)工(gōng)作(zuò)模式和(hé)從(cóng)時(shí)鐘(zhōng)工(gōng)作(zuò)模式。

(3)修改FPGA OS實現(xiàn)架構

取消FAST 2.0中UM發送端與UDO之間的FPGA OS邏輯,将UM發送端直接連接不同輸出接口的UDO模塊。取消UDO到(dào)UM的流控反壓信号,使得用(yòng)戶可以完全控制從(cóng)UM發送分組到(dào)接口MAC層輸出的延時(shí),便于支持TSN的輸出調度。

(4)擴展UDO的接口信号

在UDO的接口信号中增加與核心UM中全局時(shí)間計(jì)數器的同步信号,支持UDO時(shí)間與UM時(shí)間同步,便于計(jì)算(suàn)分組從(cóng)UM發送到(dào)接口輸出的延時(shí),用(yòng)于實現(xiàn)PTP協議(yì)分組中透明(míng)時(shí)鐘(zhōng)字段的修正。

四、下(xià)一步計(jì)劃

2019年1月底:完成FAST 3.0 UM和(hé)UDO規範草案的制定;

2019年2月底,面向TSN交換機和(hé)智能(néng)網卡控制面軟件的開(kāi)發需求,在提出對(duì)現(xiàn)有FAST的UA軟件架構進行進一步修訂的方案;

2019年3月底,基于openbox-S4完成TSN交換的基本功能(néng)演示。

歡迎關注并提出寶貴意見。

附: FAST規範的比較